## **Altera Device Package Information**

04R-00498-1.0

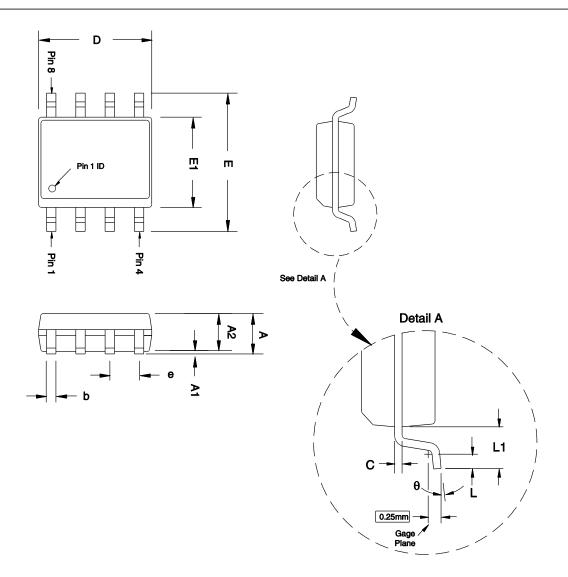

## 8-Pin Small Outline Integrated Circuit Package (SOIC) - Wire Bond

- All dimensions and tolerances conform to ASME Y14.5M 1994.

- Controlling dimension is in millimeters.

Pin 1 may be indicated by an ID dot, or a special feature, in its proximity on package surface.

| Package Information        |                                 |  |

|----------------------------|---------------------------------|--|

| Description                | Specification                   |  |

| Ordering Code Reference    | S                               |  |

| Package Acronym            | SOIC                            |  |

| Substrate Material         | Copper                          |  |

| Lead Finish (plating)      | Pb-free: Matte Tin (Annealed)   |  |

| JEDEC Outline Reference    | MS-012 Variation: AA            |  |

| Lead Coplanarity           | 0.1 mm                          |  |

| Weight                     | 0.08 g (Typ.)                   |  |

| Moisture Sensitivity Level | Printed on moisture barrier bag |  |

| Package Outline Dimension Table |             |      |      |  |

|---------------------------------|-------------|------|------|--|

| Symbol                          | Millimeters |      |      |  |

|                                 | Min.        | Nom. | Max. |  |

| Α                               | 1.35        | -    | 1.75 |  |

| A1                              | 0.10        | -    | 0.25 |  |

| A2                              | -           | -    | -    |  |

| D                               | 4.90 BSC    |      |      |  |

| E                               | 6.00 BSC    |      |      |  |

| E1                              | 3.90 BSC    |      |      |  |

| L                               | 0.40        | -    | 1.27 |  |

| L1                              |             | -    |      |  |

| b                               | 0.33        | -    | 0.51 |  |

| С                               | 0.19        | -    | 0.25 |  |

| е                               | 1.27 BSC    |      |      |  |

| θ                               | 0°          | -    | 10°  |  |

## Package Outline

## **Document Revision History**

Table 1 shows the revision history for this document.

Table 1. Document Revision History

| Date         | Version | Changes         |

|--------------|---------|-----------------|

| October 2017 | 1.0     | Initial release |

101 Innovation Drive San Jose, CA 95134 <u>www.altera.com</u> © Intel Corporation. All rights reserved. Intel, the Intel logo, the Intel Inside mark and logo, the Intel. Experience What's Inside mark and logo, Altera, Arria, Cyclone, Enpirion, Intel Atom, Intel Core, Intel Xeon, MAX, Nios, Quartus and Stratix are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Other marks and brands may be claimed as the property of others. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.