- Português

-

EnglishDeutschItaliaFrançais한국의русскийSvenskaNederlandespañolPortuguêspolski繁体中文SuomiGaeilgeSlovenskáSlovenijaČeštinaMelayuMagyarországHrvatskaDanskromânescIndonesiaΕλλάδαБългарски езикGalegolietuviųMaoriRepublika e ShqipërisëالعربيةአማርኛAzərbaycanEesti VabariikEuskeraБеларусьLëtzebuergeschAyitiAfrikaansBosnaíslenskaCambodiaမြန်မာМонголулсМакедонскиmalaɡasʲພາສາລາວKurdîსაქართველოIsiXhosaفارسیisiZuluPilipinoසිංහලTürk diliTiếng ViệtहिंदीТоҷикӣاردوภาษาไทยO'zbekKongeriketবাংলা ভাষারChicheŵaSamoa日本語SesothoCрпскиKiswahiliУкраїнаनेपालीעִבְרִיתپښتوКыргыз тилиҚазақшаCatalàCorsaLatviešuHausaગુજરાતીಕನ್ನಡkannaḍaमराठी

Controlador SSD Samsung adota arquitetura RISC-V para reduzir a dependência do braço

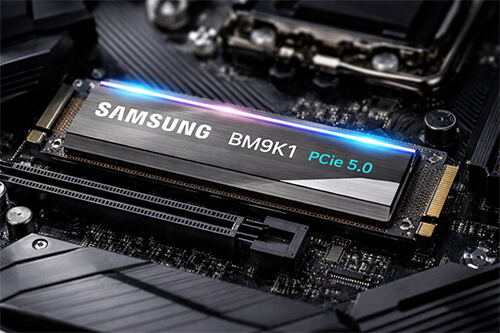

De acordo com um relatório da Wccftech, a linha de produtos SSD de próxima geração da Samsung, o “BM9K1”, utilizará um chip controlador interno e, pela primeira vez, incorporará um núcleo de CPU baseado na arquitetura RISC-V, reduzindo assim sua dependência do Arm.

O BM9K1 é o drive de estado sólido QLC de próxima geração da Samsung, apresentando um design de pacote de chip único e um lado.Graças ao suporte PCIe 5.0, o BM9K1 atinge velocidades de leitura sequencial de até 11,4 GB/s, 1,6 vezes mais rápida que seu antecessor, o BM9C1.A Samsung equipou esta unidade com um controlador interno baseado em RISC-V, que oferece flexibilidade excepcional para melhor suportar tarefas de computação personalizadas, ao mesmo tempo que melhora a eficiência energética em 23% em comparação com o BM9C1.De acordo com os roteiros de produtos, o lançamento do BM9K1 está previsto para 2027, inicialmente disponível em capacidades de 512 GB, 1 TB e 2 TB.

Atualmente, os principais processadores móveis de fabricantes de smartphones como a Samsung ainda dependem principalmente da arquitetura Arm.Por exemplo, o Exynos 2600 mais recente usa núcleos IP de CPU baseados no conjunto de instruções Armv9.3, em grande parte devido às fortes vantagens do ecossistema de aplicativos da Arm no mercado móvel, incluindo smartphones.No entanto, em áreas como sistemas embarcados e Internet das Coisas (IoT), onde a dependência do ecossistema Arm é menor, a arquitetura RISC-V de código aberto, aberta e escalável – que ganhou força nos últimos anos – tornou-se uma escolha mais vantajosa para muitos fabricantes.

O produto para o qual a Samsung está adotando a arquitetura RISC-V é um controlador SSD, que é essencialmente um processador embarcado responsável pela conversão de protocolo e transferência de dados entre o dispositivo host e o NAND Flash.Suas principais funções incluem: mapeamento de endereço lógico para físico (FTL), correção de erros (ECC), coleta de lixo (GC), nivelamento de desgaste, gerenciamento de blocos defeituosos, consumo de energia e gerenciamento térmico.

Comparado aos conjuntos de instruções Arm ou núcleos IP de CPU Arm, que exigem taxas de licenciamento, o RISC-V adota uma arquitetura de código aberto, oferecendo vantagens de custo e flexibilidade de design.Particularmente em produtos como SSDs, que apresentam altos volumes de remessas e intensa competição de preços, a adoção do RISC-V ajuda a reduzir os custos de IP a longo prazo, ao mesmo tempo que fortalece as capacidades de desenvolvimento interno.

Vale ressaltar que os controladores SSD executam firmware proprietário desenvolvido pelo fabricante, em vez de um sistema operacional que deve ser compatível com aplicativos de terceiros.Portanto, a transição da arquitetura não envolve questões do ecossistema de software;requer apenas recompilação e otimização para funcionar.Em contraste, os verdadeiros desafios residem no ajuste do desempenho e na verificação da estabilidade a longo prazo, especialmente em aplicações de armazenamento que são altamente sensíveis à integridade e latência dos dados.

No passado, a Samsung fez várias tentativas para adotar o RISC-V, mas esses esforços permaneceram principalmente na fase de demonstração ou teste.À medida que as cadeias de ferramentas e o ecossistema amadurecem gradualmente, resta saber se o RISC-V se expandirá ainda mais para mais setores de chips ou até mesmo desafiará as arquiteturas de processadores móveis.